# HEWLETT-PACKARD JOURNAL

December 1992

## HEWLETT-PACKARD JOURNAL

## Articles

| 6  | <b>A Large-Format Thermal Inkjet Drafting Plotter,</b> by Robert A. Boeller, Samuel A. Stodder,<br>John F. Meyer, and Victor T. Escobedo                 |  |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 12 | DesignJet Plotter User Interface Design: Learning the Hard Way about Human Interaction                                                                   |  |  |  |  |  |

| 16 | Electronic and Firmware Design of the HP DesignJet Drafting Plotter, by Alfred Holt Mebane IV, James R. Schmedake, Iue-Shuenn Chen, and Anne P. Kadonaga |  |  |  |  |  |

| 24 | Pen Alignment in a Two-Pen, Large-Format, Inkjet Drafting Plotter, by Robert D. Haselby                                                                  |  |  |  |  |  |

| 28 | DesignJet Plotter Chassis Design: A Concurrent Engineering Challenge, by Timothy A. Longust                                                              |  |  |  |  |  |

| 31 | DesignJet Plotter End Covers Produced by Coinjection                                                                                                     |  |  |  |  |  |

| 32 | <b>DesignJet Plotter Mechanical Architecture Development Process</b> , by David M. Petersen and Chuong Ta                                                |  |  |  |  |  |

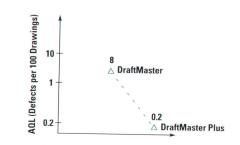

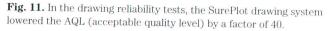

| 35 | <b>Improved Drawing Reliability for Drafting Plotters,</b> by Robert W. Beauchamp, Josep Giralt<br>Adroher, Joan Uroz, and Isidre Rosello                |  |  |  |  |  |

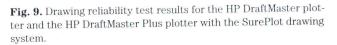

| 36 | Average User Plot                                                                                                                                        |  |  |  |  |  |

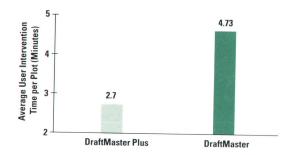

| 37 | Acceptable Quality Level Index                                                                                                                           |  |  |  |  |  |

| 42 | An Automatic Media Cutter for a Drafting Plotter, by Ventura Caamaño Agrafojo, David Perez, and Josep Abella                                             |  |  |  |  |  |

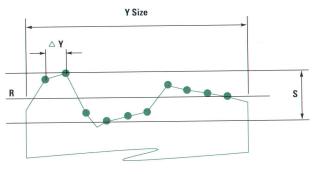

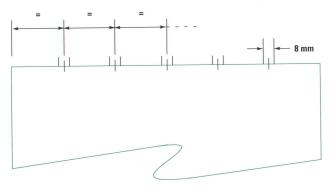

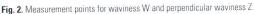

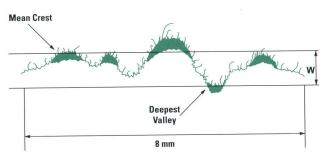

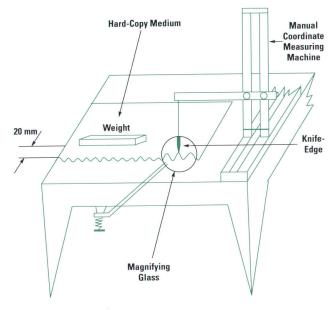

| 46 | Definitions and Measurement Procedures for Cut Quality Parameters                                                                                        |  |  |  |  |  |

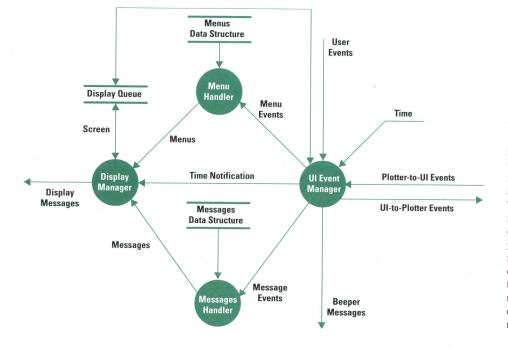

| 49 | <b>Reengineering of a User Interface for a Drafting Plotter,</b> by Jordi Gonzalez, Jaume Ayats<br>Ardite, and Carles Castellsague Pique                 |  |  |  |  |  |

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Publication Production Manager, Susan E. Wright • Illustration, Renée D. Pighini Typography/Layout, Cindy Rubin • Test and Measurement Organization Liaison, Sydney C. Avey

Advisory Board, William W. Brown, Integrated Circuit Business Division, Santa Clara, California • Harry Chou, Microwave Technology Division, Santa Rosa, California • Rajesh Desai, Commercial Systems Division, Cupertino, California • Gary Gordon, HP Laboratories, Palo Alto, California • Jim Grady, Waltham Division, Waltham, Massachusetts • Matt J. Harline, Systems Technology Division, Roseville, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Roger L. Jungerman, Microwave Technology Division, Santa Rosa, California • Bryan Hoog, Lake Stevens Instrument Division, Everett, Washington • Roger L. Sorgings Division, Colorado Springs, Colorado • Ruby B. Lee, Networked Systems Group, Cupertino, California • Bill Lloyd, HP Laboratories Japan, Kawasaki, Japan • Alfred Maute, Waldbronn Analytical Division, Weldbronn, Germany • Michael P. Moore, Measurement Systems Division, Loveland, Colorado • Shelley I. Moore, San Diego Printer Division, California • Dana L. Morrill, Worldwide Customer Support Division, Mountain View, California • Division, Moustain View, California • Dina L. Morrill, Worldwide Customer Support Division, Noutain View, California • Ginna • Dana L. Morrill, Worldwide Customer Support Division, Routain View, California • Ginna • Dana L. Morrill, Worldwide Customer Support Division, Routain View, California • Ginter Riebesell, Böblingen Instruments Division, Chermatories, Pala Altr, California • Division, Mountain View, California • Garana • Carephonerals Division, State Ross, Support Division, Mountain View, California • Gintare Riebesell, Böblingen Instruments Division, Böblingen, Germany • Marc J. Sabatella, Systems Technology Division, Fort Collins, Colorado • Sines Division, Fort Collins, Colorado • Sines Division, Fort Collins, Colorado • Sines Division, Fort Collins, Colorado • Kiness Division, Fort Collins, Colorado • Kiness

©Hewlett-Packard Company 1992 Printed in U.S.A.

December 1992 Volume 43 • Number 6

| 56  | <b>A Multiprocessor HP-UX Operating System for HP 9000 Computers</b> , by Douglas V. Larson and Kyle A. Polychronis                                   |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 58  | Next-Generation Multiprocessor HP-UX                                                                                                                  |  |  |  |  |

| 62  | Advances in Integrated Circuit Packaging: Demountable TAB, by Farid Matta                                                                             |  |  |  |  |

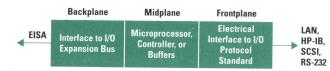

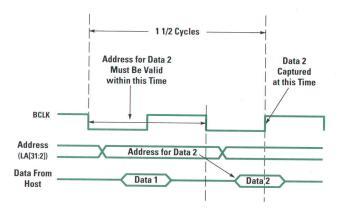

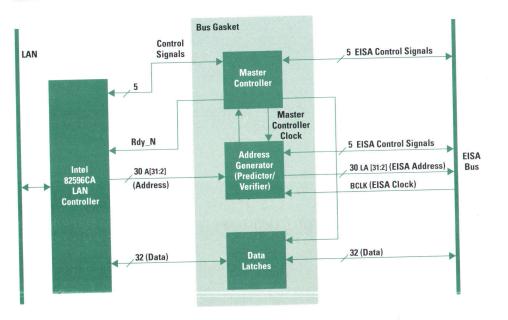

| 78  | The EISA Standard for the HP 9000 Series 700 Workstations, by Vicente V. Cavanna and Christopher S. Liu                                               |  |  |  |  |

| 83  | EISA Cards for the HP 9000 Series 700 Workstations, by David S. Clark, Andrea C. Lantz, Christopher S. Liu, Thomas E. Parker, and Joseph H. Steinmetz |  |  |  |  |

| 94  | Board-Level Simulation of the Series 700 EISA Cards                                                                                                   |  |  |  |  |

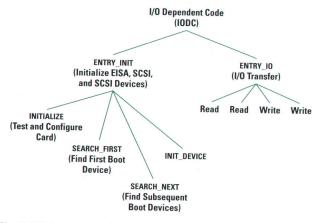

| 97  | <b>Software for the HP EISA SCSI Card,</b> by Bill Thomas, Alan C. Berkema, Eric G. Tausheck, and Brian D. Mahaffy                                    |  |  |  |  |

| 03  | Update on the SCSI Standard                                                                                                                           |  |  |  |  |

| 105 | Adapting the NCR 53C710 to Minimize Interrupt Impact on Performance                                                                                   |  |  |  |  |

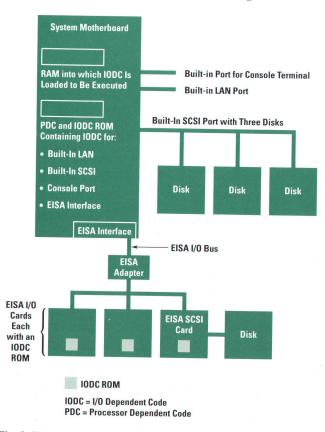

| 09  | <b>An Architecture for Migrating to an Open Systems Solution,</b> by Michael E. Thompson,<br>Gregson P. Siu, and Jonathan van den Berg                |  |  |  |  |

|     |                                                                                                                                                       |  |  |  |  |

## Departments

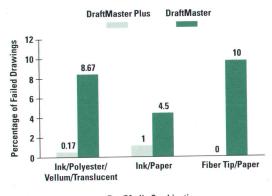

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 115 Authors

- 120 1992 Index

The Hewlett-Packard Journal is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP headquarters office in your country or to the HP address on the back cover. When submitting a change of address, please include your zip or postal code and a copy of your old label. Free subscriptions may not be available in all countries.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1992 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304 U.S.A.

### In this Issue

Drafting plotter technology occupies a good many of our pages this month, with two design groups reporting on their new large-format drafting plotters—the HP DesignJet and the HP DraftMaster Plus.

HP's thermal inkjet technology makes the DesignJet plotter as low-cost as a pen plotter and as fast as an electrostatic plotter. The pens, or print cartridges, are HP DeskJet printer cartridges, proved reliable by many years of DeskJet experience. The plotter accepts either vector commands or raster commands, uses regular drafting plotter media, and automatically cuts and stacks roll media. The article on page 6 introduces the DesignJet and discusses the issues of print

quality, media, media handling, and the user interface. The electronic and firmware design, including built-in vector-to-raster conversion and three custom integrated circuit chips, is the subject of the article on page 16. Because it wouldn't have been able to plot fast enough with one pen, the DesignJet uses two, and how it keeps the two pens properly aligned is explained in the article on page 24. The unusual chassis is a rugged, precise unit made up of low-cost nonprecision parts held rigidly in place by a cleverly designed structure (page 28). In developing the mechanical architecture, the designers found that extra time invested in communication before beginning prototype design paid off in a shorter overall project and lower-than-expected costs, as they explain on page 32.

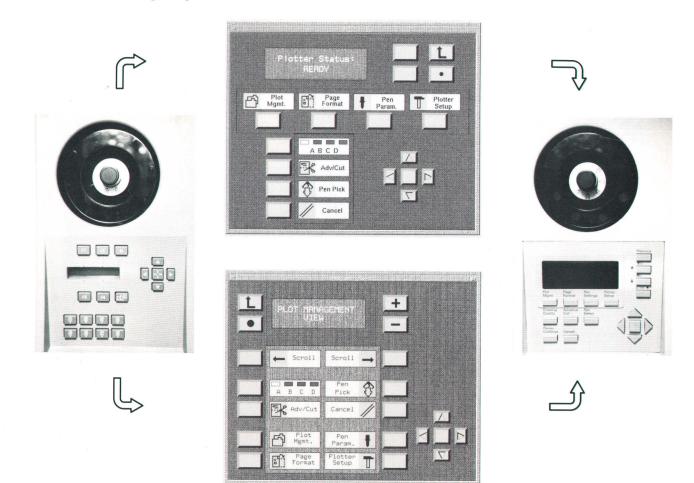

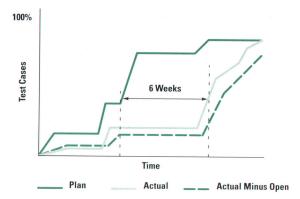

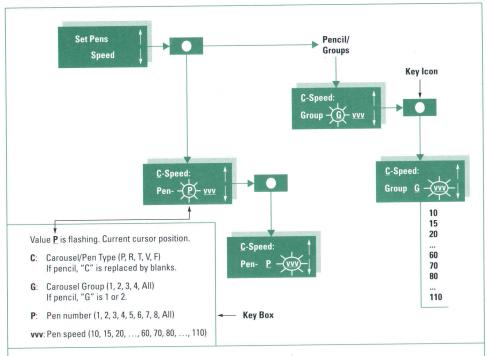

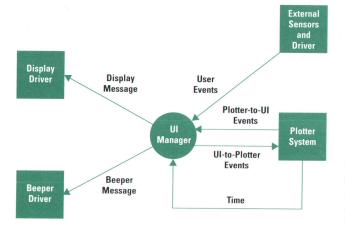

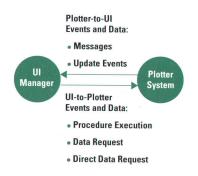

The DraftMaster Plus drafting plotter is an enhanced version of the DraftMaster pen plotter. Improved plotting reliability, improved media handling, and an improved user interface all contribute to increased user productivity by reducing the need for operator intervention during plotting. The most common customer complaints about pen plotters concern reliability—pens running out of ink, drying out, or clogging. The SurePlot plotting system includes improved pens, extra pens, and a sensor system that detects defective lines and automatically replaces faulty pens so that 998 out of 1000 drawings meet user expectations (page 35). Media handling is improved by roll feed and a new media cutter and tray (page 42). The enhanced user interface offers a redesigned front panel and simplified selection of pens, settings, and drawing quality (page 49).

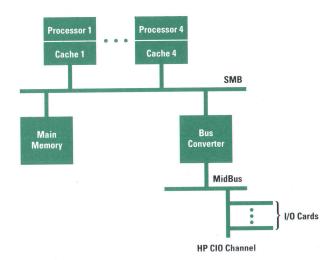

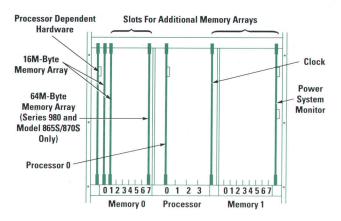

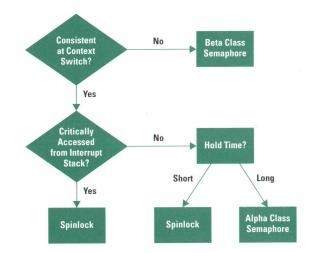

Hewlett-Packard's reduced instruction set computer architecture, called PA-RISC, provides for multiprocessor implementations in which several processors share the work. Adding a processor board to a system turns out to be a very cost-effective way of improving the performance of a computer system, particularly for online transaction processing (OLTP). The operating system schedules the processors and keeps them from interfering with each other. The first multiprocessor implementation of the PA-RISC architecture supports up to four processors and is available in versions that run either the HP-UX\* operating system or the MPE/iX operating system. The article on page 56 tells how the HP-UX kernel was modified to support multiprocessor operation and shows how much the performance is improved by adding processors. A feature of multiprocessor HP-UX is that, unlike many multiprocessor operating systems, it can run on a uniprocessor system with no performance penalty.

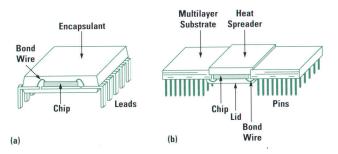

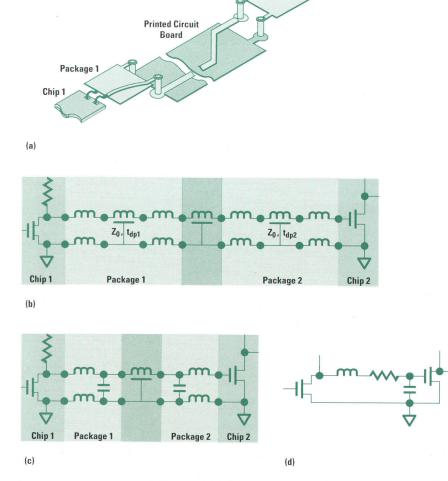

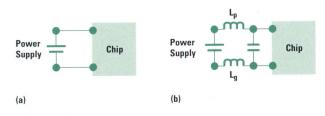

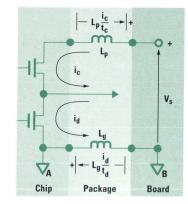

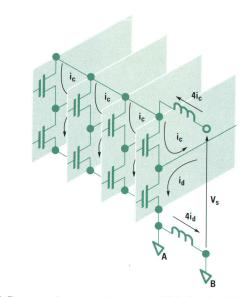

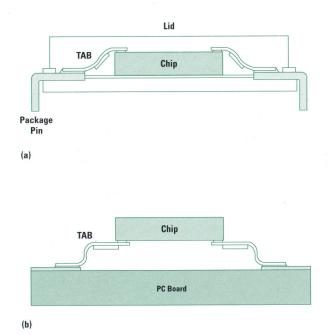

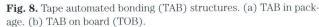

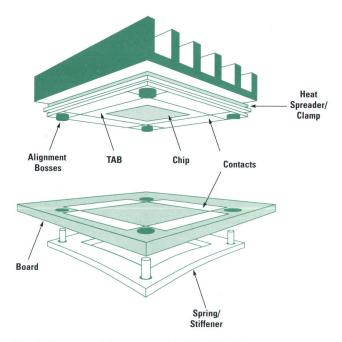

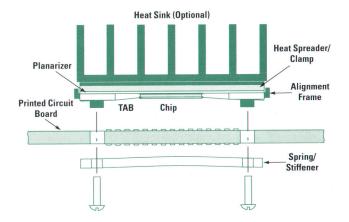

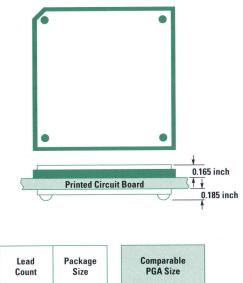

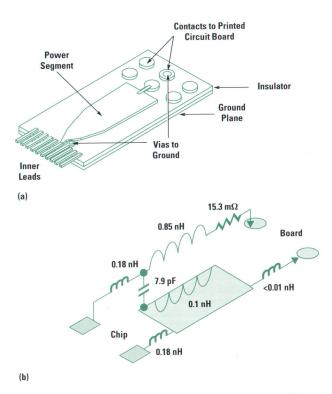

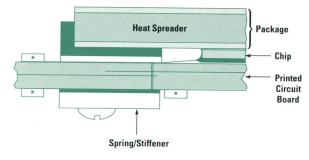

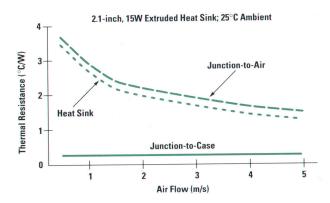

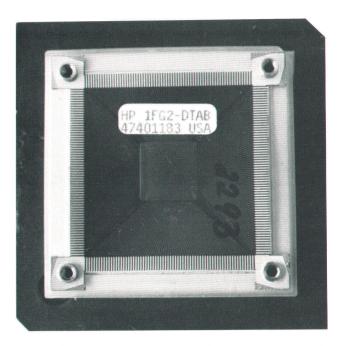

State-of-the-art very large-scale integrated circuits like microprocessors can contain millions of transistors and have hundreds of inputs and outputs. For various technical and logistical reasons, such chips are rarely mounted directly on printed circuit boards, but instead are supplied in packages, which are soldered onto the boards. While some packages provide high-performance electrical and thermal environments and some are easy to assemble and rework, the ideal package would meet all of these requirements. A packaging technology that comes closer to the ideal than any of its predecessors is described in the article on page 62. Based on an existing technology called tape automated bonding, or TAB, it maintains TAB's advantages of good performance and lower cost, but doesn't require TAB's expensive facilities and is easy to demount and rework. Called demountable TAB, or DTAB, it was developed by HP's Integrated Circuits Business Division.

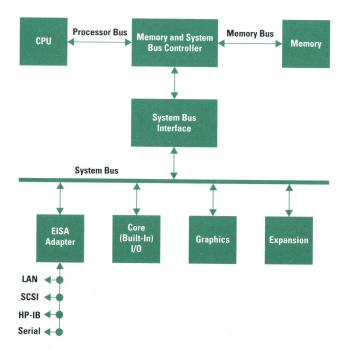

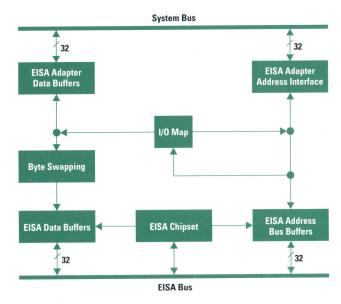

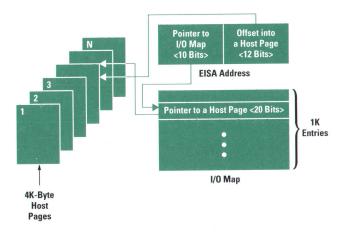

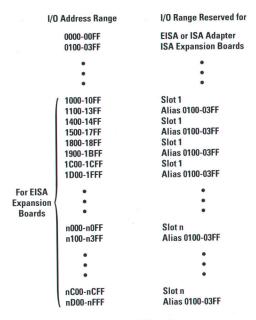

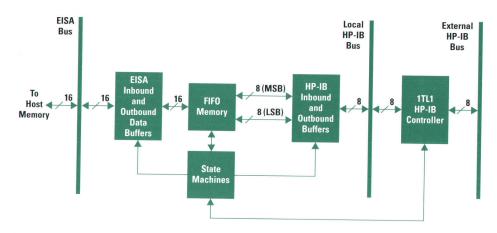

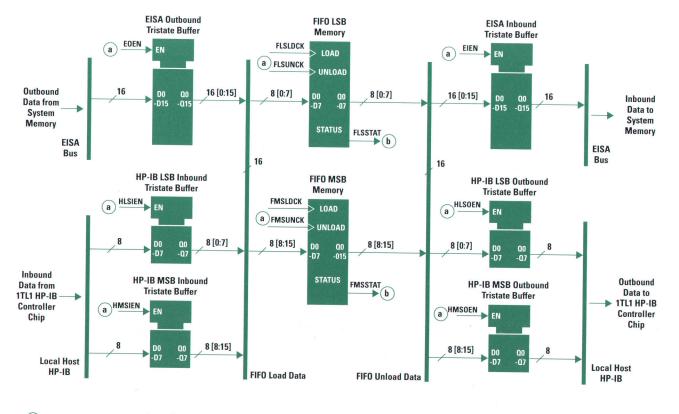

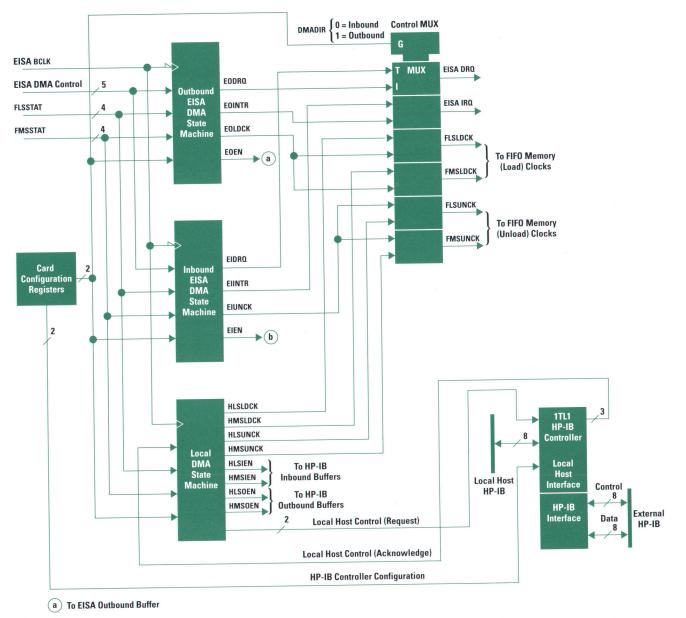

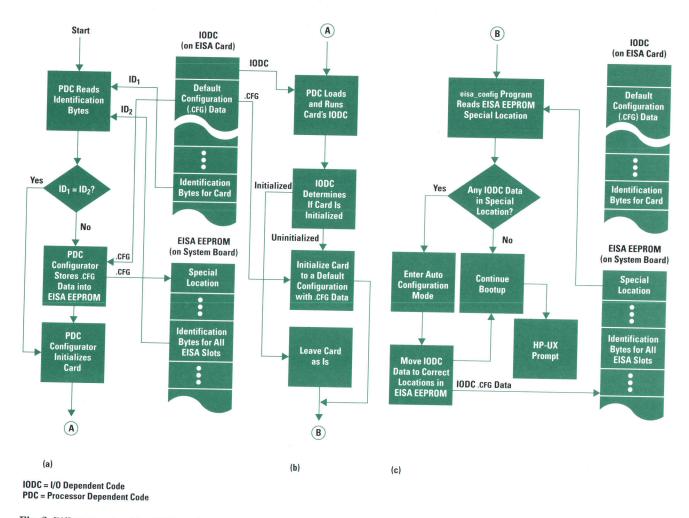

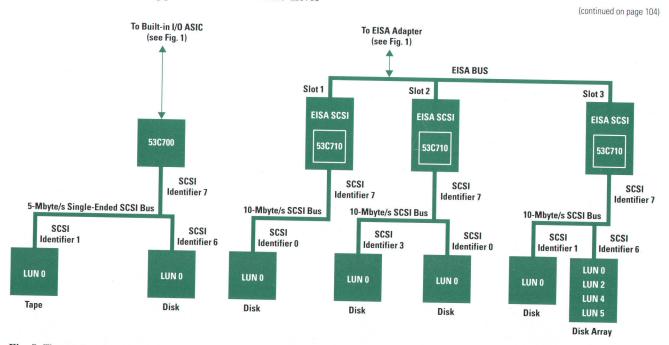

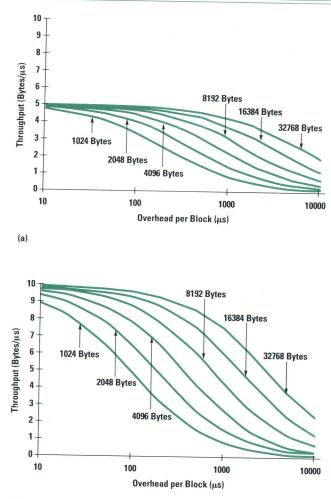

As explained in our August 1992 issue, the HP 9000 Series 700 computer workstations have a built-in, or core, input/output system that provides a variety of industry-standard I/O ports. Because many customers will need higher performance or want to expand their systems, the Series 700 workstations also offer an I/O expansion bus, which accepts plug-in cards that provide additional industry-standard I/O ports. The EISA bus (EISA stands for Extended Industry Standard Architecture) was selected for the Series 700 expansion bus because it is a high-performance bus that is expected to meet the needs of HP customers and because it meets HP's goal of converging to an industry-standard I/O bus for all new workstations. The article on page 78 describes the adapter that provides the EISA bus to the outside world, acting as a bridge to the internal Series 700 system bus. Four types of plug-in EISA I/O cards are now available for the Series 700: an IEEE 802.3 (Ethernet) LAN card, an IEEE 488 (HP-IB) card, a SCSI (Small Computer Systems Interface) card, and a programmable serial interface card. Discussed in the article on page 83, the cards use EISA bus master and DMA (direct memory access) methods to take advantage of the EISA burst-cycle protocol for high-speed data transfer. The software for the EISA SCSI interface card is explained in the article on page 97, which also talks about recent extensions to the SCSI standard.

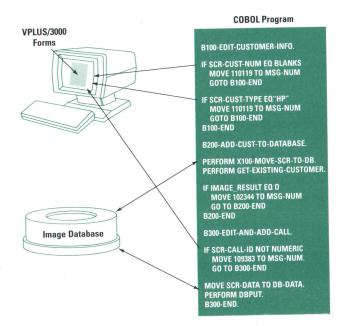

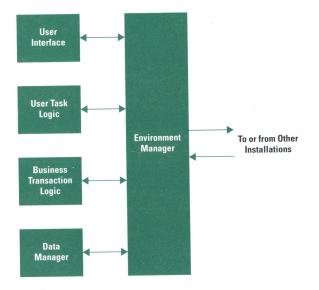

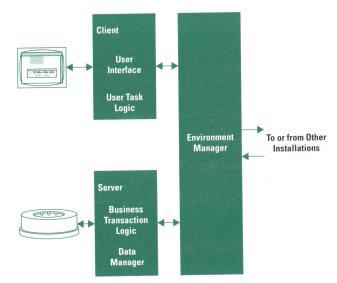

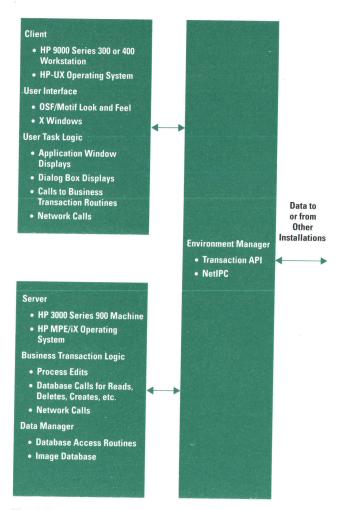

The article on page 109 is from HP's Worldwide Support Systems (WSS) organization, where they develop mission-critical systems for HP's worldwide customer support business. Seeing the emergence of client/ server solutions based on open systems concepts, WSS began to migrate their applications to this new paradigm while it was still in its infancy and standards were still being defined. They developed a technical architecture that provides a framework for designing modern, integrated client/server applications. The article explains the architecture and relates WSS's experiences in migrating two existing applications.

December is our annual index issue. The 1992 index starts on page 120.

R.P. Dolan Editor

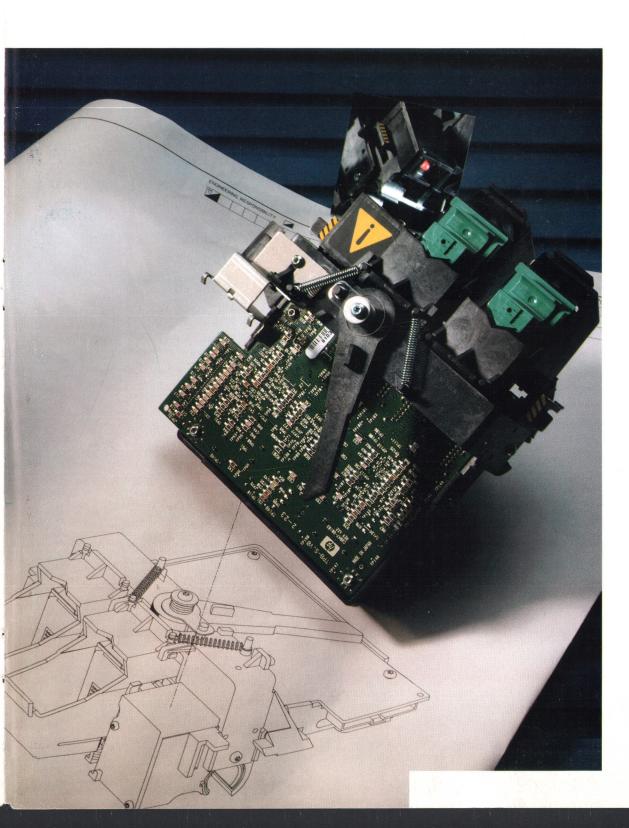

### Cover

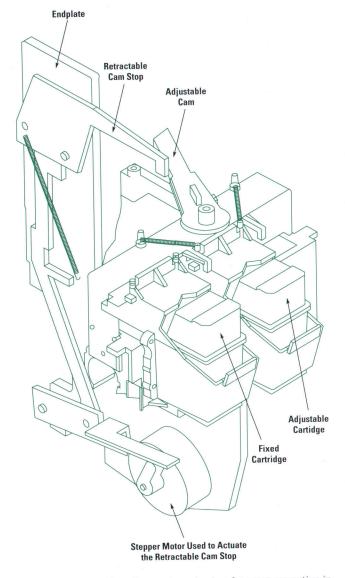

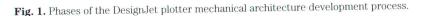

The pen carriage of the HP DesignJet large-format thermal inkjet drafting plotter is shown with a DesignJet plot. The two print cartridges (HP DeskJet printer type) can be seen, as can the lever or adjustable cam that is part of the mechanism for aligning the pens in the media direction (scan direction alignment is done by adjusting pen-firing timing). The red light-emitting diode (in the mirror) is part of the adjustment system—it illuminates a test line that's used to measure and correct pen misalignment. (The mirror isn't part of the pen carriage. We just put it there to show the LED. We also simulated the LED light for this photo.)

### What's Ahead

The February issue will be entirely a lightwave technology issue, featuring articles on the design of the following fiber optic test instruments:

- HP 8504A precision reflectometer

- HP 8146A optical time-domain reflectometer

- HP 83440 Series lightwave detectors

- HP 8167A and 8168A tunable light sources

- HP 81534A return loss module for the HP 8153A lightwave multimeter.

Leading off the issue will be a paper summarizing the contributions of HP Laboratories' photonics research program to HP's lightwave product line.

HP-UX is based on and is compatible with UNIX System Laboratories' UNIX\* operating system. It also complies with X/Open's\* XPG3, POSIX 1003.1 and SVID2 interface specifications.

UNIX is a registered trademark of UNIX System Laboratories Inc. in the U.S.A. and other countries.

X/Open is a trademark of X/Open Company Limited in the UK and other countries.

## A Large-Format Thermal Inkjet Drafting Plotter

The HP DesignJet drafting plotter combines the low cost of pen plotters with the speed of electrostatic plotters. Throughput is almost independent of drawing complexity. The plotter uses the same roll and sheet media as pen plotters, and in roll mode, automatically cuts and stacks plots for unattended operation.

## by Robert A. Boeller, Samuel A. Stodder, John F. Meyer, and Victor T. Escobedo

The major contribution of HP's first large-format drafting plotter, introduced in 1981, was high performance at a much lower price than had previously been available. Through the application of HP's proprietary inkjet technology, the new HP DesignJet large-format drafting plotter offers customers the same kind of contribution in performance at low cost while providing greater reliability of the ink delivery system and greater user friendliness.

The DesignJet plotter (Fig. 1) can plot a complex D-size drawing in three minutes on commonly available media. It is

**Fig. 1.** The HP DesignJet plotter uses thermal inkjet technology to produce large-format plots on commonly available drafting media. A roll-feed mode allows unattended plotting with automatic cutting and stacking of completed plots. Resolution is 300 dots per inch and plot time for a D-size plot is about three minutes.

quiet and can produce several hundred plots without a pen change. It accepts single sheets or, for unattended plotting, a roll of media. When a roll is used, a built-in cutter separates the plots into sheets, which fall into a media tray below the plotter. The plotter accepts vectors (HP-GL/2 instructions) or raster data (HP Raster Transfer Language). Resolution is 300 dpi.\*

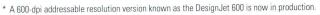

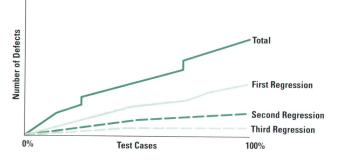

Low-cost plotting has been dominated by the traditional pen plotter. Pen plotter performance is usually characterized in terms of acceleration and velocity. The greater the complexity of the image, the longer it takes to plot. An architectural plot on E-size paper might be in the range of 100,000 to 1,000,000 vectors. A typical throughput profile for a 4g, 25-ips plotter might look as shown in Fig. 2.

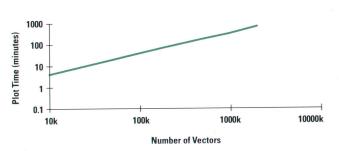

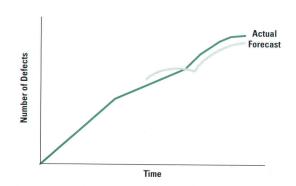

In contrast, the DesignJet plotter's performance does not change much with drawing complexity. Throughput is more a function of the page size and the vector transmission and conversion time. The DesignJet plotter's built-in Intel 80960 processor and electronic architecture make vector transmission and conversion time very small. A typical throughput profile for the DesignJet plotter is shown in Fig. 3.

HP inkjet technology also provides customers with an improvement in writing system reliability. The inkjet pens each hold about 38 cc of ink, and no priming is needed when starting up. The DesignJet plotter uses two pens, which will last for about 200 reasonably complex E-size plots. The plotter can be left unused for many weeks, and the writing system will always work without intervention when it is needed.

Fig. 2. Pen plotter plot time as a function of plot complexity.

**Fig. 3.** HP DesignJet plotter plot time as a function of plot complexity and size.

The DesignJet plotter represents a major contribution towards making a large plotter more friendly. Sheets and rolls load easily from the front of the machine and are ejected toward the front, making plot retrieval easy. The built-in cutter works well on all media types, including Mylar, which is usually a challenge because of its silica content. A passive media stacking system stacks up to 20 plots.

The DesignJet plotter is one of the first HP products to incorporate a modular I/O slot that will allow many HP peripherals to use the same I/O cards. At the product's introduction, there were MIO (modular I/O) cards available that allow the DesignJet plotter to connect to some networks and to HP-IB (IEEE 488, IEC 625) systems. The MIO strategy promises to provide our customers with a much broader range of connectivity solutions as new cards are developed.

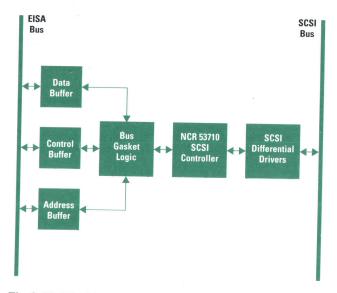

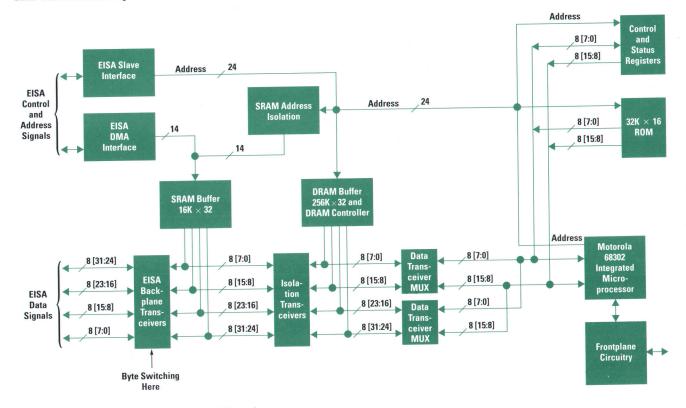

#### **Design Challenges**

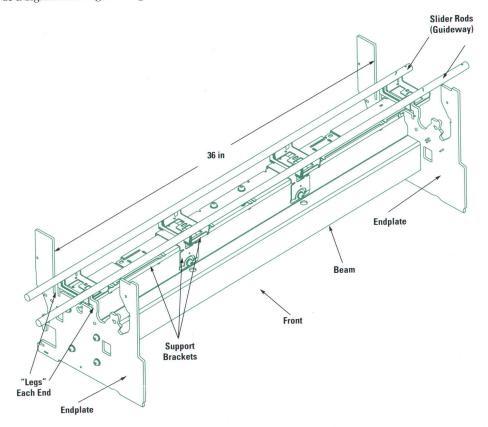

We knew that print quality is our customers' most important need. But larger-format plotters require very tight tolerances over the large distances required to span an E-size sheet of paper. Unfortunately, the laws of physics dictate that large beams lose their stiffness rapidly as they get longer. Therefore, we had to engineer the product right from the beginning to be stiff enough and accurate enough to hold the required tolerances.

To increase the plotting throughput, the DesignJet plotter incorporates two pens instead of just one. Two pens can print twice as fast as one, but must be aligned accurately, so that the customer does not see any banding or gaps at the junction between pens. The same throughput requirement put demands on the vector-to-raster converter that transforms the HP-GL/2 input into the raster data that the pen needs.

We needed to make a major improvement in the ease of using and loading the machine. Large-format plots are difficult to handle, and our goal was to try to make the plotter as easy to use as an HP DeskJet printer. We also needed a way to stack plots as they came out of the machine.

We needed to make the machine reliable so that it could be used unattended. This required careful design of the media path and the cutter system so that paper would never jam or tear and the machine would be guaranteed to work all the time without user intervention.

We needed to be very cost conscious, and this required care in meeting design-for-assemblability and design-formanufacturability goals. It also created a need to integrate more of the electronics.

We had a tremendous number of functions to implement in the firmware. Some of this functionality provides compatibility with other HP plotters, such as front-panel control of line types and widths. Other functionality provides new opportunities for using the plotter, such as our RTL (Raster Transfer Language), which allows vectors and raster data to be mixed on the same plot, and our MIO support, which allows the plotter to be used on a network directly, without connecting through a server.

#### **Major Features**

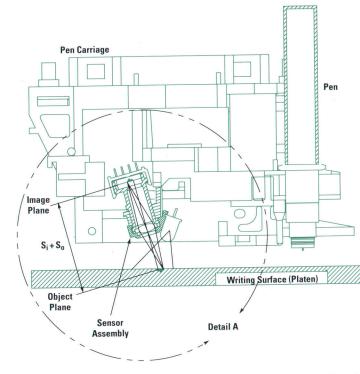

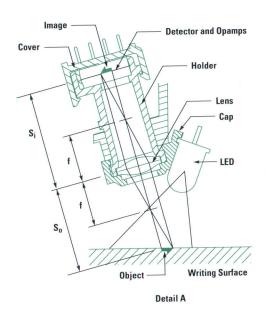

The DesignJet pen carriage holds two print cartridges, along with a mechanism that allows one of the cartridges to move slightly relative to the other so that optimal print quality can be achieved. The carriage also holds optical sensors for automating this adjustment and for automatically detecting the paper edges.

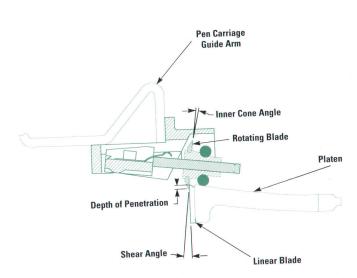

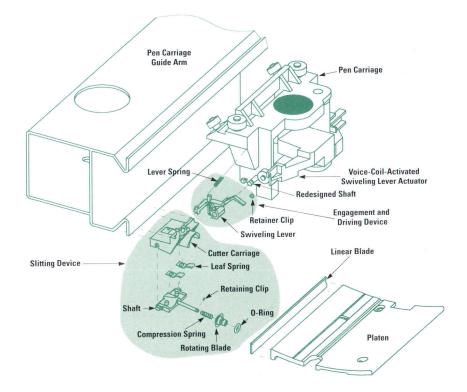

The Y-axis drive servo system, which moves the carriage back and forth on precision rails, includes a linear encoder for maximum accuracy. The same Y drive also programmatically engages a separate cutter carriage that cuts roll-feed media. The media cutter consists of a carriage-mounted rotary blade that is spring-loaded against a fixed linear blade.\*

A pen service station caps the inkjet cartridges to prevent the ink from drying out when the plotter is not in use. The service station includes a wiper to help maintain a clean nozzle surface, which helps print quality. Also included is an ink-drop detector, which is used to determine if the cartridge is firing properly.

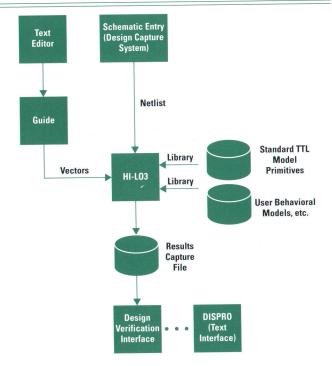

The X-axis drive servo system moves the media. The media drive system can handle a wide range of media widths up to 36 inches, and is also capable of driving a wide range of media types. A precisely dimensioned rubber roller provides a friction drive.

The roll-feed assembly accepts rolls of media up to 50 meters in length. A sheet stacking system collects the plots as they are cut off the roll.

#### System Block Diagram

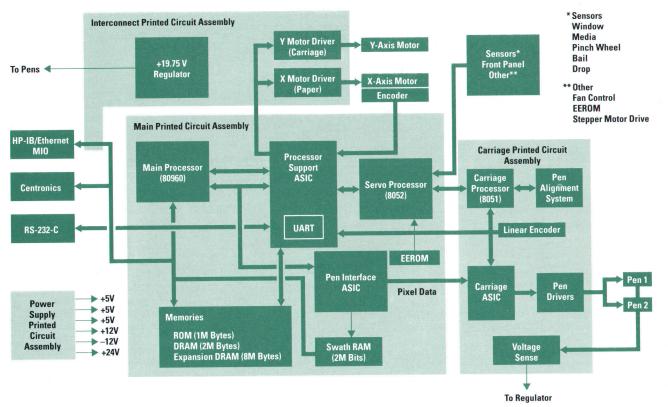

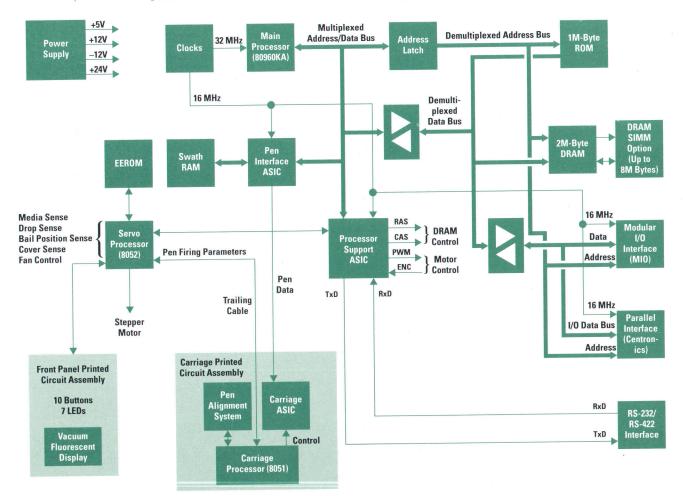

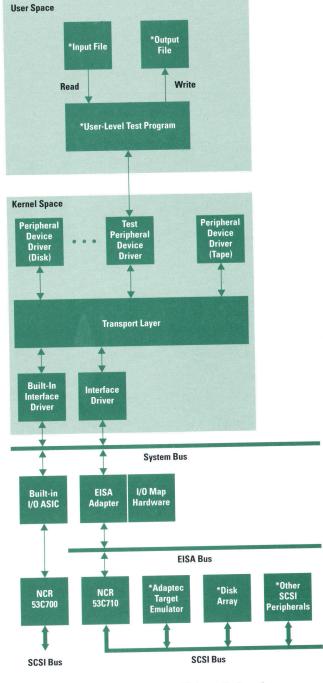

The DesignJet plotter block diagram, Fig. 4, shows the relationships of all of the major functional areas of the plotter.

The cutter design is similar, but not identical, to the media cutter of the HP DraftMaster Plus plotter (see article, page 42).

Fig. 4. Simplified system block diagram of the HP DesignJet plotter.

The input/output ports are treated as memory addresses. The RS-232 universal asynchronous receiver/transmitter (UART) is part of the processor support ASIC (applicationspecific integrated circuit). There are three ASICs in the DesignJet plotter.

1M bytes of system read-only memory (ROM) is used to store system firmware. 2M bytes of dynamic random-access memory (DRAM) is standard. Expansion slots allow expansion of the DRAM to 10M bytes. 2M bits of RAM is used to store swath information. An electrically erasable read-only memory (EEROM) IC is used as nonvolatile memory to store variables that must be retained when power is off.

DRAM addressing is controlled by the processor support ASIC. The main processor, an Intel 80960, communicates with the servo processor (an 8052) through the processor support ASIC, since the two processors run at different clock frequencies.

The pen interface ASIC removes swath pixel data from the swath RAM and transfers the data to the carriage ASIC, which is located on the pen carriage printed circuit assembly, through the trailing cable. The carriage ASIC creates the proper signals for the pen drivers.

The processor support ASIC receives encoder feedback data from the X-axis and Y-axis motors and outputs the data to the servo processor for calculation of the necessary pulse width modulation (PWM) signals to drive the motors. The processor support ASIC outputs the PWM signals to the motor drivers, which are located on the interconnect printed circuit assembly.

Front-panel and all sensor input (except the line sensor) goes to the servo processor, which also controls the fan, the stepper motor that moves the pen nozzle wiper blade, and the EEROM. A voltage regulator on the interconnect printed circuit assembly controls the pen drive voltage.

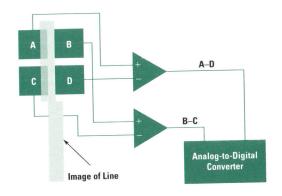

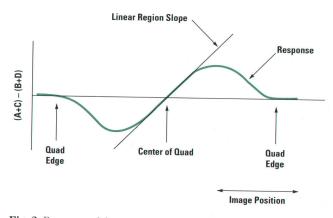

The pen carriage line sensor output goes to an analog-todigital converter (ADC), which outputs the converted signal to the carriage processor (an 8051).

## **DesignJet Print Quality**

Good print quality is of prime importance for any printer or plotter. An understanding of the customers' print quality needs and how to meet them was critical to the success of the DesignJet plotter.

During the investigation phase of the DesignJet project both internal and external surveys were conducted to determine how well a large-format, monochrome, thermal inkjet plotter would be perceived by the target market. Pen plotter, electrostatic, and inkjet plots were shown to customers. Customer comments on print quality were recorded and categorized. Next, specific print quality attributes were identified and special surveys were conducted to quantify what specifications had to be achieved to meet the customers' needs. These special surveys included media and print mode testing, banding, vertical line straightness, and cockle testing.

#### **Media and Print Mode Testing**

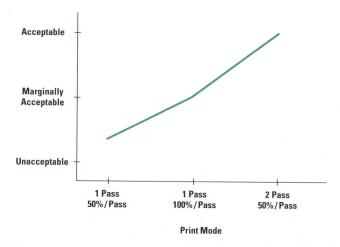

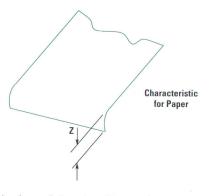

The target market is primarily composed of pen plotter users who need higher throughput. These users prefer to use the media types that are commonly available today for pen plotters. We found that most commonly available plotter bond papers exhibited excellent print quality when printing with one pass of the inkjet pen over the paper. However, when printing area fills on some vellums and translucent media, two passes of 50% ink density per pass were required before customers would consider the samples to be finalquality plots (see Fig. 5). The two-pass print mode worked quite well to improve the uniformity of area fills. Commonly available polyester film media did not work well even with multiple passes. Therefore, a special film that is more receptive to the ink was developed to work with a two-pass print mode.

#### **Banding and Line Straightness**

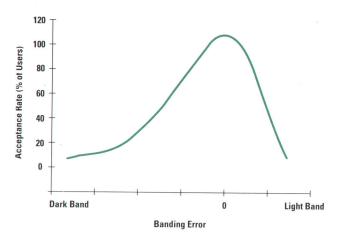

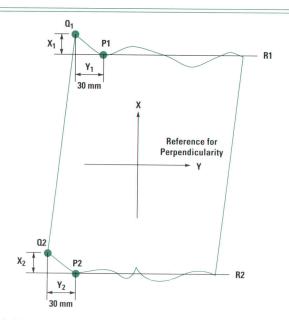

To determine what were acceptable limits for banding, a survey was designed to test user sensitivity to this print quality attribute. Plots were generated on a highly accurate drum printer. Adjacent swaths were printed with known displacements from the ideal. This resulted in a range of plots, each with a different level of discrete swath boundary misalignment (bands). When adjacent swaths are placed too far apart a light band or gap is visible and when adjacent swaths are placed too close together a dark band or overlap appears. Users were asked to rank the plots for acceptability (see Fig. 6). By evaluating the survey data we were able to determine how accurate the specifications for the printing mechanism would have to be in the paper axis direction.

Line straightness was tested in much the same way. Plots were printed with discrete offsets at swath boundaries in the direction of swath scan. By evaluating the survey results, we were able to determine how accurate the specifications for the printing mechanism would have to be in the pen scan direction.

#### **Cockle Testing**

Cockle is the wrinkled appearance of paper after having being soaked in water and then left to dry. The high water content of the HP DeskJet pen ink results in significant cockle when applied in large area fills. Analysis of customer plots showed that most users do not plot with high print densities. However, solid area fills are used for small logos and thick lines.

To better understand user sensitivity to cockle, a test was designed to determine how dense a plot could be and still have acceptable cockle. Plots were printed with a pattern of evenly spaced square area fills. Area size and spacing were varied from plot to plot. Users were then asked to rank the

Fig. 6. Plot acceptability as a function of banding error.

plots for cockle acceptability. The survey results showed us that for area fill sizes and spacing that would be typical for our target market, there would be no problem with cockle.

#### **Design Issues and Technical Risks**

After the primary print quality specifications were established based on user needs, the design effort commenced to find ways to achieve these goals at the lowest possible cost. Key elements of the design were closely analyzed and risks were balanced. Worst-case analysis was done early to prove that various concepts could meet the required error budgets. The areas in which it was most difficult to meet the required specifications were banding and line straightness.

Banding error is the sum of errors caused by paper advance accuracy, pen-to-pen alignment in the paper axis, and failed or weak pen nozzles. The banding tolerance specification is taken up mostly by pen-to-pen alignment and paper advance errors.

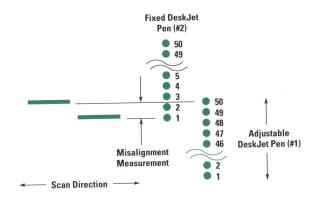

On the DesignJet plotter, two DeskJet printer pens are used essentially as one larger pen to meet throughput goals. Worst-case analysis of the pen carriage tolerances and Desk-Jet pen tolerances showed that this concept would result in banding because of pen misalignment in the paper axis, and that the banding would be much greater than the customer would tolerate. An automatic pen alignment system was designed to minimize the amount of error budget consumed by pen alignment.

The allowable error remaining for the paper advance system resulted in a considerable design challenge. Several alternative designs were analyzed using Monte Carlo simulation methods. The winning concept uses an indexing worm drive gear transmission scheme. This approach virtually eliminates cyclical errors caused by the motor, encoder, and worm pinion. To reduce the errors caused by variation of the effective diameter of the drive roller, a calibration is performed on the production line using the DesignJet's own internal reference.

Achieving the line straightness goal also proved to be a difficult task. The DesignJet plotter not only requires two Desk-Jet pens to act as one larger pen but also needs to print bidirectionally to achieve the throughput goals. Much attention had to be given to the alignment of the pens in the scan direction to achieve the vertical line straightness goal. A scheme was implemented by which pen alignment error in the scan direction and bidirectional error (carriage deadband) are measured with an optical sensor. These errors are then corrected by varying the timing of ink-drop firing.

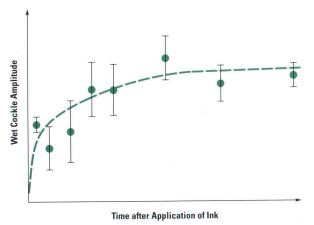

The difficulty arose when we tried to align pens that exhibit excessive spray along with the main ink drop. The effects of spray on alignment get worse as the pen-to-paper distance increases, but moving the pens close to the paper risked the possibility of a pen drag because of cockle in a high-inkdensity plot. The problem was minimized by doing a careful worst-case analysis of the pen-to-paper distance and moving the pen as close to the media as possible. Cockle amplitude was measured as a function of time for paper and translucent bond to determine how close the pen could be to the paper without any possibility of touching (see Fig. 7).

As mentioned above, cockle dictates how close the pen can be to the paper, which ultimately affects line quality. To minimize cockle, the paper path is designed to constrain the paper physically as much as possible. The paper is wrapped around a drive roller and is tensioned by an overdrive roller. In this way, paper cockle in the printing area is forced to a high-spatial-frequency, low-amplitude state, allowing the pen to be located as close as possible to the paper.

#### **Production Control of Print Quality**

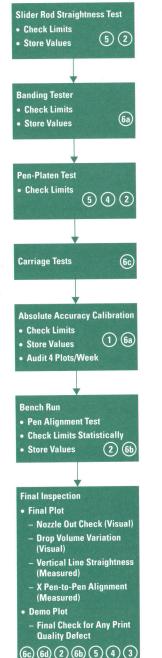

Meeting print quality goals is dependent not only on careful design but also on careful production control to ensure that no product is shipped that does not meet all print quality specifications. On the DesignJet production line, several tests measure the performance of each machine for each print quality specification (see Fig. 8).

The banding specification is checked by four tests. First, cyclical errors in the paper drive are automatically measured and then analyzed with an FFT (fast Fourier transform) algorithm. From this data, a faulty part in the drive train can be identified and replaced. Second, accurate paper movement is ensured by an absolute accuracy calibration test. Next, weak or faulty pen firing is checked by visual examination of a test plot. Lastly, print cartridge alignment in the paper direction is measured with the aid of a video

Fig. 7. Measurements of wet cockle (paper wrinkling after being wet and dried) as a function of time.

Fig. 8. Assembly line print quality attribute control for the HP

microscope measurement system. Vertical line straightness is also ensured by measuring a print sample with the video

Proper pen height above the paper is checked by two separate tests. First, slider rod straightness is measured as part of the chassis assembly procedure. Second, pen-to-paper distance is measured directly for each machine by installing a height gauge in the pen stall and measuring the distance to

DesignJet plotter.

microscope system.

the platen at three different locations.

#### **Print Quality Attribute Specifications**

- 1. Accuracy

- 2. Line Straightness

- 3. Margin Parallelism

- 4. Line Fuzziness

- 5. Wet Cockle/Pen Smear

- 6. Banding

- a. Swath Advance

- b. X Pen Alignment

- c. Nozzle Out

- d. Drop Volume Variation

The final check for print quality is done by human inspection of a demonstration plot at the last station on the assembly line.

## DesignJet Media

The media set plays an important part in the customer acceptability of a plotter. It was a requirement that the Hewlett-Packard media recommended for the new Design-Jet thermal inkjet plotter provide consistent high quality, equal to or better than other brands on the market. The project goal was to use the current Hewlett-Packard pen plotter media set for the DesignJet plotter, the only exception being the drafting film. This goal presented a challenge in two areas: opaque bond paper and vellum.

#### **Opaque Bond Paper**

The then-current Hewlett-Packard bond was being changed concurrently with the development of the DesignJet plotter because of Hewlett-Packard environmental concerns and media archivability issues with the existing acid-process bond paper. A project had been initiated to develop a new alkaline plotter bond paper that would be better for the environment, provide improved archivability, and have superior print quality. Adding the requirement to support a thermal inkjet plotter increased the complexity and risk of the project and necessitated meeting the more aggressive plotter development schedule.

A major impetus for this alkaline paper project was the environmental issue. Alkaline paper processes use chemicals that are less harmful to the environment. Paper companies were changing their "plain papers" to alkaline partially in response to this concern. Plotter papers were not being considered for this change by the majority of plotter paper manufacturers, but we felt that Hewlett-Packard should be among the leaders in this effort.

Pen plotter and thermal inkjet inks have water as a major component. In typical pen plotter inks, water makes up slightly more than half of the ink. Other cosolvents are present depending on the type of pen and the manufacturer. In thermal inkjet ink, water makes up 90% or more of the ink. The cosolvent, while a much smaller percentage of the total ink mixture, is much more aggressive. The challenge in developing an alkaline paper that is compatible with both pen plotter ink and thermal inkjet ink involves the basic components of the paper sheet.

The common plotter papers were and still are typically acidprocess and were developed to meet the requirements of pen plotter inks. This means a moderately high level of internal sizing compared to plain papers such as office paper or copy papers. Surface control of the image components of the ink is important to maintain fine line quality. Pen plotters emulate manual drafting methods, using pen strokes to create the lines and structures. Therefore, controlled removal of the solvents (water and others) from the surface of the sheet is not as critical as it is for the DesignJet thermal inkjet plotter.

Alkaline papers use the same paper fibers as acid paper and the process is very similar, using the same paper machine equipment. Alkaline papers differ from acid papers in two major areas: sizing and fillers. Sizing imparts water resistance along with other properties to the paper either through internal sizing or surface sizing. Fillers are used to fill spaces between the paper fibers, to improve printability, and to replace the more expensive paper fibers. The filler of choice for alkaline papers is calcium carbonate, and for acid papers the filler typically used is clay.

Extensive testing of alkaline sizing agents indicated that their water resistivity is equal to or better than that of the acid sizing agents. Therefore, sizing did not appear to be the critical component. The next component of paper to evaluate was the calcium carbonate. Sample papers with varying amounts of calcium carbonate were evaluated with both pen plotter inks and thermal inkjet inks. The level of calcium carbonate in the paper sheet was inversely proportional to the print quality level of both pen plotter and thermal inkjet plotter output. Controlling the calcium carbonate level improved print quality but the improvement was not sufficient for Hewlett-Packard products, so sizing was revisited.

The last component considered was the surface sizing. Our paper manufacturer had been working concurrently on paper components to improve thermal inkjet performance on alkaline papers. The particular surface sizing component developed for other products was tested on our candidate paper, and resulted in improved control of the thermal inkjet ink on the surface of the paper. This provided the needed improvement in print quality to make the paper acceptable.

The final effort in developing the paper was to characterize the current media, understanding the requirements of pen plotters and thermal inkjet plotters, and then recreate the physical characteristics of the acid paper in the alkaline paper. Rigorous testing of the then-current acid paper was performed to develop the model to present to the paper manufacturer. Testing included all image and handling characteristics of the paper sheet. These included both media handling characteristics such as thickness, stiffness, surface smoothness, surface friction, tear strength, tensile strength, and moisture and image characteristics such as opacity, brightness, paper color, and porosity.

The model was presented to the paper manufacturer along with a plotter test bed. As a result of the early investigation and the investment in developing a detailed model of the sheet, the new alkaline opaque bond met all the print quality and schedule requirements for both pen plotters and the new DesignJet plotter. Print quality for the DesignJet was optimized and critical performance parameters such as media handling, color response, and sheet feeding for pen plotters were maintained or improved.

#### Vellum

The vellum presented a different challenge. Developmentphase testing of the DesignJet plotter with the vellum resulted in marginal performance because of the characteristics of the new improved thermal inkjet ink. Thus a new vellum was necessary to meet the print quality goals. The DesignJet schedule required a successful vellum within six months.

(continued on page 13)

## DesignJet Plotter User Interface Design: Learning the Hard Way about Human Interaction

How many times have you picked up a product and found it easy to use? If a product is easy to use, it probably was no small task to make it that way. With some products, even simple ones, I can be frustrated because I can't make it do what I expect it to do. Either I don't know how or it doesn't have the capability. The manual may be within reach but I have no interest in consulting it. With any product, users hope to combine their own intuition with external clues to determine the machine's capabilities and correct operation. What a confidence builder it is when a person can walk up to a new machine and operate it correctly!

We engineers, with our generally analytical minds, think that the simple solution is to publish a manual with step-by-step instructions. Although users expect such a manual, at least 50% will attempt operation without even opening it. Apparently users do not find it pleasant to build their mental model of a machine's operation by using only diagrams and text from written instructions.

Although the cause is noble, achieving intuitive operation is not so easy. A designer, familiar with each intricacy of the mechanism, will express an opinion and come up with the initial user interface design. Is this going to work for all users? I think not, but it is a place to start.

Our brain is parallel processing input from five senses and filtering it through past experiences. No amount of analytical thinking in a serial fashion can possibly predict the human response. The designer's experience with the development precludes any useful help in the user interface area. Perhaps, we might think, an experienced person could help us determine how people will react. Mistake! No one person can determine the best user interface that will appeal to the most people. This is a very difficult concept. When your manager tries out your design and has a certain difficulty, that can seem like the highest-priority problem, but it may just be a corner case. User testing is the key.

The DesignJet plotter started life as a gleam in the eyes of an architectural team. Prototypes were built, and along with proving the functionality came early user testing of some of the concepts the designers were concerned about. For example, to load roll media, the user needed to preselect roll format on the front panel, place the roll correctly on the spindle (it can go four ways), insert the media into the load slot, and lift the pinch roller release lever to align. Was the roll-to-spindle orientation intuitive? Would people lift the lever when instructed by the front panel?

The designer's opinion was that we needed to redesign for automatic lever lift; we should not be asking people to raise the lever. Mistake! No one person, especially the designer, can determine user reaction. A week's worth of investigation resulted in an unacceptable impact to cost and schedule and so the idea was reluctantly shelved. Later user testing showed that people had no problem or frustration when the display read "Lift lever." They simply lifted the only lever on the machine.

The same initial user testing showed that all users intuitively oriented the roll on the spindle backwards. This sent us into another redesign, this time for two months, resulting in a prototype that allowed the roll to be installed this way. Mistake! Users look for clues and parallel process all information. This new prototype displayed a new set of problems of both function and ease of use. Going back to the original design, a more subtle change was made. A graphic label installed under the roll cover was the clue that users were looking for. It was only in the absence of any other information that they showed the opposite preference for roll orientation.

With the initial concerns addressed by user testing, we thought we could continue with hard tooling. Mistake! Not all user interface problem areas can be predicted. The entire system must be tried by typical users not familiar with the product.

Testing after hard tooling revealed that people will not select sheet or roll mode before trying to load the media. Initially a button on the front panel toggled two light-emitting diodes that displayed the type of media the DesignJet plotter expected. From the previous problem, we had already learned that the DesignJet did not need to be redesigned; we simply had to provide more clues. Now, after the load is initiated, the plotter pauses and asks the user, by means of the front-panel display, to select which format of media has been loaded. This tested well and has the added benefit of providing the user with time to stop and decide (with hands off) if the plotter has a good, even grip on the media before continuing. Unfortunately in this case, the hard tooling needed to be modified as an unexpected expense.

At the same time, it was found that first-time users almost always created a paper jam while trying to load. This was, of course, unacceptable. Observation of user tests showed the various techniques people were using to load. The DesignJet plotter grabs the media after a set amount of time when the media passes a sensor in the insertion slot. People did not know that they needed to wait for this time and then let go of the media so that it could move into the mechanism. We needed to provide some clues. An audible click, which was part of the original concept, was not enough. Almost by accident, it was discovered that if we moved the media quickly at the start, users would instinctively let go.

Another problem was that some people were using a line on the side of the machine to adjust the media squareness. People complained that there needed to be a guide on the side to align the media. It wasn't until we thought about the comment that we realized this was how they expected to keep the media square. They were frustrated because the DesignJet would reject that load as misaligned. It was not possible to use the marks on the side to adjust the squareness. Our other plotters use a side surface to reference the media and these people were accustomed to that type of system. The correct DesignJet method is to push the media against the pinch rollers which are, unfortunately, out of sight. The lines on the side were only an approximate left/right location reference. Within 1/4 inch of the side line would have been fine. Our solution was to reduce the length of the line on the right so it didn't look like something to align to and to add a label in the area that explains in six different languages to "Push media against rear stops." A better solution might have been to make the pinch rollers visible to the user.

The position selected for the label is not very eye-catching but has the benefit of not cluttering the appearance of the machine. While looking at this solution, the general comment was, "No one will ever see it." Mistake! Don't ask people to predict how others will perceive. User testing of first-time users showed that they were unsure of how to load and were actively searching for clues. Almost all noticed and comprehended the label. A bail lift timing change bought us some extra design margin which, combined with the improved user interface, gave us a vastly improved and acceptable design.

The design might be improved further now that we have gained a clearer understanding of DesignJet user perceptions. But to give an accurate model of user perception, user testing requires a complete product, and a complete product is not receptive to many changes. This creates a minor dilemma neatly expressed as: "In every product's development, there comes a time when you must shoot the engineer and go into production." In my case the wound was not fatal and I'm recovering nicely.

> P. Jeffrey Wield Design Engineer San Diego Technical Graphics Division

The manufacturing of a translucent 100% cotton vellum results in internal and surface characteristics different from those of bond paper. The vellum has an added resin component that fills in the voids between the fibers to impart the translucency to the sheet. This results in a sheet that has essentially no porosity compared with the relatively porous plotter bond. This further reduces the ability of the ink solvents to migrate into the sheet. In addition, some transparentizers, as the resins or oils are called, are not compatible with the thermal inkjet inks. The project required understanding the thermal inkjet ink chemistry interactions with various transparentizers and selecting the best transparentizer for the best print quality on pen and thermal inkjet plotters.

As with the bond paper, extensive testing of the existing vellum was undertaken to determine the desired physical characteristics. The data was used to develop a model for the vellum similar to that for the bond paper. The vellum manufacturer used this information to develop a vellum that not only provides excellent print quality on the thermal inkjet plotter but also has improved characteristics on pen plotters.

These products, along with the remainder of the media set, were exhaustively tested under a variety of environmental conditions on the DesignJet plotter to ensure Hewlett-Packard quality for our customers.

## DesignJet Media Bin

The Designjet plotter provides "unattended plotting." This involves handling multiple output sheets with no user intervention. The user should be able to pick up a finished plot without the added inconvenience of unrolling and hand-cutting a plot, or picking it up from the floor. We needed to go beyond the usual catch tray, which could wrinkle or damage the plot. The DesignJet plotter provides an automatic oneaxis cutter that will trim the plot to the right length after plotting from a roll. The trimmed sheets are then handled by an automatic sheet stacking system that won't damage the plots. This function is provided at a low cost increment.

#### **System Requirements**

To define the media stacker requirements, we conducted user surveys, surveys of the media distributors, and focus group studies. From the collected data, we created a typical user model and determined the following requirements for the media stacker:

- It should work with popular media from most manufacturers.

- It should work with media sizes from C size or equivalent up to E size or equivalent.

- It should work with all media types, including vellum, chart paper, translucent, and polyester film.

- It should work under a wide range of environmental conditions.

- It should not exceed the footprint of the machine because of space constraints in the office environment.

- It should have low incremental cost.

- It should stack up to 20 sheets without user intervention.

Because it would have been impractical to test all of the possible media permutations, we defined a representative media sample from the most popular manufacturers to be evaluated and tested.

#### **Design Considerations**

Cost, time, and available resources pointed toward a passive system. This implied that system performance would be heavily influenced by the behavior and properties of the media.

We identified the critical properties that would affect a passive system and then proceeded to characterize these properties at extremes of temperature and humidity because the physical properties of most media types change drastically under different environmental conditions. We also looked at the inherent properties of roll media, since rolls are the media format used during unattended plotting (cut-sheet mode requires the user to load and remove plots individually, unlike roll mode, in which plots are automatically cut and stacked).

#### **Media Properties**

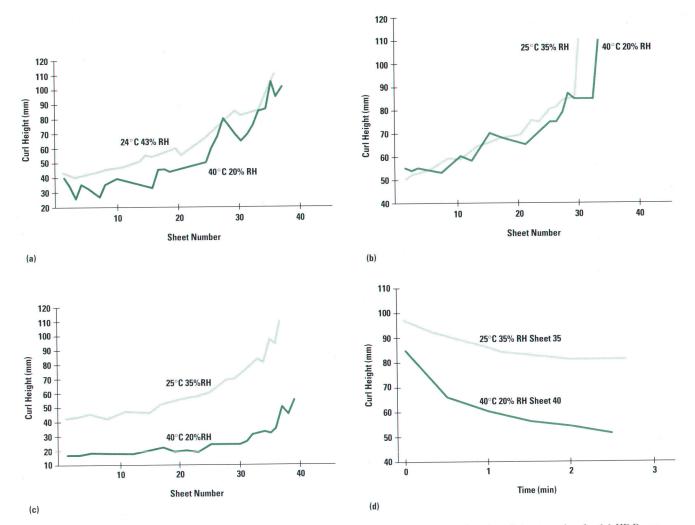

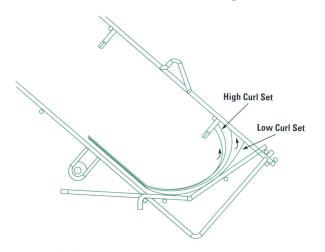

Curl-Set. Curl-set is curvature induced in the media because of internal stresses as it is deformed to wrap around the core of the roll. This induced curvature is more pronounced closer to the core because it is proportional to the radius of the core and the tension used to wind the media around the core. We characterized curl-set as a function of sheet position within the roll, and we also measured curl-set relaxation as a function of time. Curl-set is affected by temperature and humidity, so we tested at extreme environmental conditions (see Fig. 9). A section of roll media with curl-set so pronounced that it tends to roll on itself once the sheet is cut is considered not stackable. We found that the stackable portion of the media roll varies considerable from roll to roll, and from media type to media type. It appears that many media vendors do not have good control over rollwinding tension, which affects curl-set directly, so different rolls vary from 100% to 60% in the percentage of their length that is stackable. The amount of curl-set relaxation over time is not enough to make a difference in media performance.

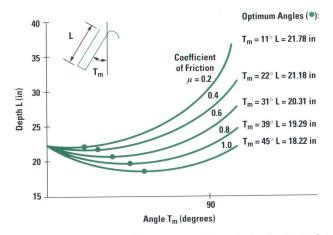

**Friction**. We measured the friction coefficient of the representative samples to try to determine the optimal slide angle for this type of stacking system. Fig. 10 shows curves of tray depth as a function of slide angle for 44-inch sheets. The optimum angle is where the depth is a minimum. This angle varies with the coefficient of friction.

**Ink Dry Time.** The ink dry time is the time required for the ink to dry once it is applied to the media. This is an important parameter because we needed to be sure that the ink will be dry by the time it touches the ramp of the media stacker or other sheets, so that the plot won't smear.

**Stiffness.** The rigidity of the sheet as it is feed from the plotter to the stacker affects the geometry required to guide the media properly. Moisture content affects stiffness to a considerable extent. Some media samples could collapse before being stacked because of reduced stiffness.

#### **Geometry and Operation**

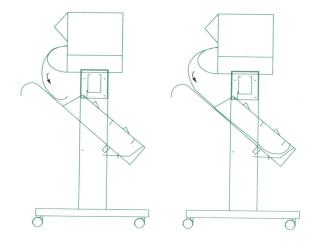

To keep the media stacker bin within the limits of the plotter footprint, we devised a ramp that inverts the sheet direction under the machine.

**Fig. 9.** Curl-set and curl-set relaxation measurements for various media types. Curl height as a function of sheet number for (a) HP Paper (b) JRG vellum V-20 (c) Clearprint 1000H vellum. (44-inch sheets. Sheet 1 is on the outside of the roll.) (d) Curl height as a function of time for Clearprint 1000M vellum.

The principle of the system is to guide the sheet using a ramp at a relatively steep angle into a stop. The sheet is then allowed to form a loop outside the ramp as it is fed, so that when the sheet is cut, the weight and position of the loop induce it to fold outward, so that half of the sheet ends up

Fig. 10. Measurements of depth versus slide angle for the DesignJet media stacker.

inside the bin and the other half hangs on the outside. Subsequent sheets follow the same path and are stacked on top of the previous sheets (see Fig. 11).

To handle curled media from a roll, we devised a feature close to the bottom of the bin to serve as a stop for the curling media. If the media is considerably curled, the leading end of the sheet will tend to curl on itself. When the sheet is cut, it will collapse into a roll. The stop feature stops the leading edge before it curls on itself (see Fig. 12).

The parameters that have a first-order effect on stacking are bin depth, the position of the bin relative to the output gap, and inclination angle of the ramp. These parameters can be optimized for a particular media type and length of sheet. Unfortunately, there are large variations in media properties and dimensions. We compromised the geometry of the system so that it would function with the most popular combinations of media type and sheet length, and we provide a three-level depth adjustment to handle different sheet lengths.

Fig. 11. Operation of the DesignJet media stacker.

#### Acknowledgments

The DesignJet development team was highly dedicated, professional, and motivated. The team members worked together well and respected the values that each area of expertise brought to the program. In addition to the people mentioned in other articles in this issue, the authors would like to thank the following for their notable contributions beyond the call of duty: Alecia Jay and Nancy Helff for the great manuals

Fig. 12. Curl stop functioning.

and user need studies, Dan Goese, Andy Tallion, and Steve Flack for the great marketing support they gave the program, Sharon Jensen, Joe Milkovits, Dan Caputo, Russ Bergen, Rob McCline, Rick Hermes, Katherin Ault, Scott England, Carey Enslow, Nancy Huelsmann, Adrian Huges, Nils Madden, Vinh Nguyen, Richard Szapacs, and Warren Werkmeiser for the excellent job they did in working with our suppliers and making sure that quality and delivery were priorities, Rod Degesero for the product packaging, which has proven itself capable of standing up to the worst transportation abuse, Irene Caravantes, Mike Duffy, Sandra Boldt, Vern Hudson, Cameron Light, Donna Ogilvie, Virginia Pollack, Jusitine Prehatney, Carey Ramos, Bob Stuart, and Christine St. Ives for the work they did in creating market visibility and market support for the product, Peter Morris, Bruce Mueller, and Allison Rap for getting our consumables in place, Rick Brown and Andy Tricario for the production support they gave during the design phases, and Stephen Glass, Tracie Middleton, Scott Bonnet, Tom Barker, and Scott Roleson for the excellent role they played in making sure the product met worldwide agency approvals and in ensuring that the product meets customer expectations. Glenn Gaarder, Don Hiler, Lynn Palmer, Jeff Stong, Darren Wilcox, and David Walker are additional mechanical engineers who contributed to the program greatly.

## Electronic and Firmware Design of the HP DesignJet Drafting Plotter

High-performance vector-to-raster conversion and print engine control are provided by a RISC processor, two single-chip processors, and three custom integrated circuits. Development of the electronics and firmware made extensive use of emulation and simulation.

## by Alfred Holt Mebane IV, James R. Schmedake, Iue-Shuenn Chen, and Anne P. Kadonaga

The HP DesignJet raster inkjet plotter project required contributions in the design of vector-to-raster conversion and print engine electronics. The project was constrained by cost and schedule, but the performance of the vector-toraster converter and the inkjet print engine was considered of prime importance in meeting our user's needs. Our traditional approach to plotter electronics, while meeting cost and schedule goals, would have fallen short of the required performance goals. Existing electrostatic vector-to-raster converters, while meeting performance goals, were too expensive for our market. The approach we took was a fresh look at the requirements of both the vector-to-raster converter and the print engine.

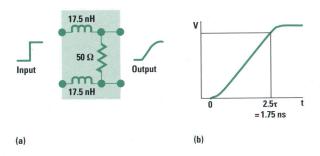

#### Vector-to-Raster Converter

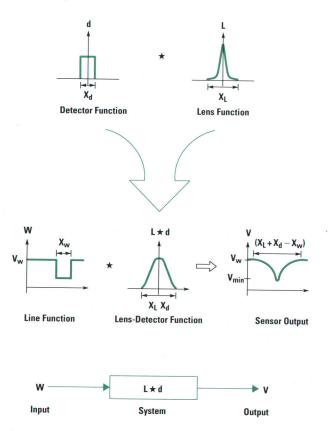

Two major tasks are performed by the vector-to-raster converter. The first is HP-GL/2 language parsing. The second is conversion of the parsed objects into the dot patterns printed on the page. In the DesignJet plotter, these two tasks are serial and do not occur simultaneously.

Fig. 1. Electronic block diagram of the HP DesignJet large-format inkjet drafting plotter.

An early decision was made to include the vector-to-raster converter in the base machine electronics even though several low-cost competitive raster products omit this feature. The design team felt that a vector-to-raster converter could be integrated together with the print engine control logic at a reasonably low incremental cost. The major constraint placed upon this implementation was that it be of high enough performance to outpace the print engine in all but the most complex plots. It was acceptable to slow the print engine during very complex plots, but only for the affected carriage scans.

Initial investigations centered on the use of specialized graphics processors. These processors were more than adequate for the rasterization of lines, but were far too slow when parsing HP-GL/2. Next, an approach was investigated in which a general-purpose processor performed the parsing and print engine control while a graphics processor did only the raster conversion. The fundamental weakness of this approach is the cost of using two processors even though only one is required at any point in time.

The final design is based on a single, high-performance, RISC processor for both print engine control and the two vector-to-raster converter functions. The selection criteria were cost, a performance benchmark based on an existing HP-GL/2 parser, and an engineering estimation of potential raster conversion performance. The Intel 80960KA was selected from the available choices, which included both RISC and CISC microprocessors. Although they were not part of the original criteria, two other features of the 80960KA made it attractive in the DesignJet application. The first of these is the multiplexed address and data bus, which reduced the pin count on the application-specific integrated circuits (ASICs) that were being designed for the product (see "DesignJet ASIC Development" on page 18). The second is the existence of the 80960KB processor, which includes hardware floating-point capability. If at any time during the project the need for faster floating-point performance had arisen, the -KA version could have been replaced by the -KB version without any circuit board changes.

The remainder of the processor portion of the electronics consists of 2M bytes of DRAM, 1M byte of ROM, I/O, and DRAM memory expansion. A processor support ASIC in this section provides a DRAM controller, wait state timing for both RAM and ROM, interrupt control, and 80960 reset synchronization. This ASIC is described later in this article.

Fig. 1 is the electronic block diagram of the HP DesignJet plotter.

#### Input/Output

The DesignJet plotter was originally defined as a plotter solution for pen plotter users who require greater throughput on monochrome plots. This definition suggested incorporation of the three built-in I/O ports—RS-232-C, HP-IB (IEEE 488, IEC 625), and printer parallel—that are included in existing HP plotters. The DesignJet R&D team decided to pursue a more flexible approach. A strategy that had been adopted for the LaserJet IIISi printer was investigated in which there is no built-in I/O but instead a standardized, modular I/O slot (MIO) capable of accepting many different types of I/O options. After reviews with manufacturing and service representatives it was decided to keep the RS-232 and parallel interfaces built-in to allow the DesignJet plotter to leverage existing test and repair systems. The built-in HP-IB port has been replaced with an MIO slot to allow the DesignJet plotter to use some of the I/O options developed for the LaserJet IIISi. At introduction both the HP-IB and Novell Ethernet were available options.

#### **Memory Expansion**

One of the more difficult specifications to set for the Design-Jet plotter was DRAM memory size. In a pen plotter, each vector is strobed out as it is received, so plotting can begin as soon as the first vector is parsed. The DesignJet plotter must parse and store all the incoming vectors before making the first carriage sweep. It is an inconvenient feature of vector languages that the last vector received may cross the portion of the page covered by the first carriage scan. This leads to a limitation on plot complexity based on the memory size available to store parsed vectors. The trade-off is the cost of memory versus the complexity of the possible plotted images. Hewlett-Packard electrostatic plotters solve this storage problem by means of magnetic disk storage. The drawbacks of a DesignJet implementation of a similar solution were cost and the difficulty of providing a mechanical mounting to allow a disk drive to survive the shipping and operating environments expected for the DesignJet plotter. The chosen solution is industry-standard, 72-pin single inline memory modules (SIMMs). This memory is added in the form of 1M-byte or 4M-byte SIMMs, which are available from HP for a variety of products in the personal computer and peripheral areas. Two sockets are available under a panel in the rear of the plotter. Addition of two 4M-byte SIMMs gives a user an additional 8M bytes of vector storage for complex plots. The use of SIMMs for memory expansion adds very little cost for users with needs fitting into the standard 2M-byte RAM and provides a relatively low-cost upgrade path for users requiring more.

#### **Print Engine Control**

Print engine control is a much less demanding task than vector-to-raster conversion. Print engine control includes two-axis servo motor control, front-panel control, keyboard scanning, front-panel display update, optical sensor scanning, and thermal inkjet pen service station control.

The servo motor control functions of position decoding and pulse width modulation of the motor voltage were added to the processor support ASIC. The other functions required mostly pins with very little logic, so alternatives were investigated that could implement them more efficiently. The result of this investigation is an approach that surprised most of the design team. A single-chip processor, the Intel 8052, was able to perform these functions with a lower production cost than an ASIC and for a fraction of the development cost. It also performs all of the real-time servo control, offloading this from the 80960KA.

The 8052 is designed into the architecture as a slave processor to the 80960KA. A bidirectional command and mailbox port is implemented in the processor support ASIC to allow processor-to-processor communication. Through this port the 8052 is able to return data to the 80960KA in response to commands or to generate one of several interrupts. Among these interrupts is the operating system time slice interrupt.

A vast portion of print engine control is the electronics required to support the thermal inkjet pens. The most difficult function performed in this area is the mapping from the image generated in memory by the vector-to-raster converter to the series of timing pulses sent to fire the pens. This task is made difficult by the fact that the DesignJet plotter uses two 50-nozzle pens that are not accurately aligned mechanically with each other. The mapping and alignment compensation are performed by two ASICs, one located on the main board and a companion part located on the circuit board that travels on the pen carriage. The two ASICs are connected by a serial link that runs through the trailing cable. The pen interface ASIC on the main board is initialized with the measured distances between the two pens and is able to select from image memory all the dot positions that are covered by pen nozzles at a given carriage position. As the carriage scans across the page, this ASIC sends groups of 100 bits up the serial link to the carriage ASIC at 1/300-inch intervals. The carriage ASIC buffers the 100 bits and creates the timing patterns used as inputs to the drivers that generate the firing waveforms for the thermal inkjet pens.

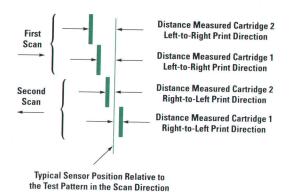

#### **Pen Calibration**

Offsets between the two pens are measured by another set of electronics located on the carriage board (see article, page 24). DesignJet pens are aligned by drawing a series of patterns on a page and then using an optical sensor to measure the relationship of patterns drawn with one pen to the patterns drawn by the other. These offsets are written to the thermal inkjet support ASICs as described in the paragraph above. The electronic components of the optical system are controlled by an 8051 microprocessor located on the carriage board. The decision to use the 8051 on the carriage is based on the same criteria used to select the 8052 for the main board—the 8051 can perform the sensor control functions at a lower part cost and a much lower development cost than a special-purpose ASIC. An added feature gained by using the 8051 is that it provides the serial communication path to the 8052 on the main board. This communication path is used

both for the optical system and for sending pen firing constants to the ASIC on the carriage.

### **DesignJet ASIC Development**

Often the custom IC design is in the critical path of electronic systems development. This was the case for the HP DesignJet plotter project. Three ASICs were needed to provide the necessary functionality and performance in the DesignJet plotter at a low cost.

The main challenges were clear right from the beginning. The team had to deliver three working ASICs on schedule. A turnaround in any of the ASICs would have meant a serious schedule slip, since the fully functional ASICs were needed to start much of the system-level testing. The team also had to provide the functionality of these ASICs before the first silicon became available to enable parallel development of the printer mechanisms and firmware. These needs had to be met with a limited number of engineers and a given budget to avoid adversely affecting other projects.

#### **Processor Support ASIC**

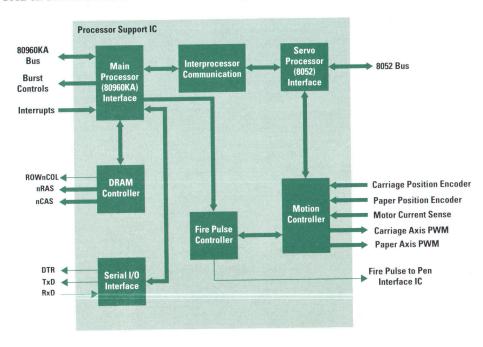

The processor support ASIC interfaces to both the main processor (80960KA) and the servo processor (8052) and performs various assist functions for each processor. The block diagram of the IC is shown in Fig. 2. The main processor side of the processor support ASIC consists of the 80960KA interface, the DRAM controller, the serial I/O interface, and the fire pulse controller. On the servo processor side, the IC contains the 8052 interface and the motion controller. The processor support ASIC also provides two modes of communication between the processors: a polled, bidirectional mailbox and an interrupt-driven, unidirectional block transfer buffer.

The 80960KA interface assists the processor during burstmode ROM and DRAM accesses and handles the queueing and prioritizing of the incoming interrupts. The DRAM controller supports up to 20M bytes of memory of different sizes

**Fig. 2.** Processor support ASIC block diagram.

and access times. The serial I/O interface consists of a baud rate generator and a UART (universal asynchronous receiver/ transmitter). The fire pulse controller generates a synchronizing pulse for each column of pen data. The output is extrapolated from the carriage position encoder counts at one, two, or four times the frequency.

The motion controller decodes the position information for the carriage and paper axes. It also generates the PWM (pulse width modulation) signals for the dc motor drivers as needed for servo control of the carriage and paper axes. A watchdog timer monitors the servo loop and disables the PWM outputs in the event of a servo processor malfunction. A status register is also provided to log various motion control error conditions.

#### **Pen Interface ASIC**

A shuffler stage is needed to map the row-oriented image data into the column-oriented DeskJet pen nozzle data. In a departure from previous shuffler designs, the pen interface ASIC uses a dedicated external memory array to store its own copy of the image data and a programmable internal sequencer array to hold the shuffle pattern. The shuffling is done by copying an entire swath of image data from the system memory into its local memory and fetching the pixel data for each pen fire sequence according to the preloaded shuffle pattern. This approach offloads these tasks from the main processor bus and allows greater flexibility for supporting different pen nozzle configurations.

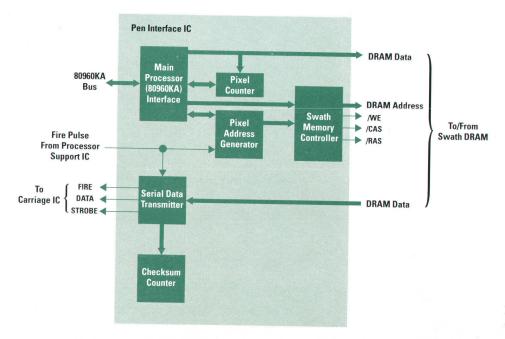

The pen interface ASIC contains three bus interfaces: the main processor (80960KA) bus, the swath memory interface, and the serial link to the carriage ASIC. The block diagram of the pen interface ASIC is shown in Fig. 3. In the copy mode, the data and address path from the main processor interface to the swath memory is enabled. The pixel counter counts the number of pixels to be printed, and its output is used to calculate the plot density and ink use. In the shuffle mode, the path from the swath memory to the serial interface is enabled. The serial data transmitter assembles the

pixel data fetched from the swath memory for each fire sequence into a serial bit stream and sends it to the carriage ASIC. The pen interface ASIC and the carriage ASIC contain identical pixel checksum counters to check the integrity of the serial transmission.

The pixel address generator is the heart of the pen interface ASIC. It consists of an SRAM array for the programmable sequencer, a logical column counter, and an adder. The sequencer is preloaded with the pixel address offsets for each pen nozzle of a fire sequence. The offsets contain the column adjustment delays for pen alignment correction (see article, page 24). A mask pattern is tagged onto each entry to aid different print modes. The column counter is either incremented or decremented depending on the print direction, and its content is added to the pixel address offset from the sequencer to generate the physical DRAM address of each pixel's data.

#### **Carriage ASIC**

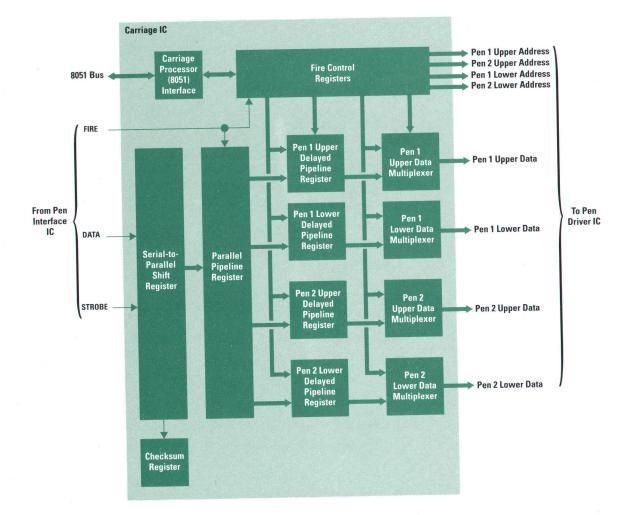

The carriage ASIC resides on the printed circuit board that is mounted on the moving pen carriage assembly. Its primary function is to generate the data and address signals for the pen driver ICs. The relative timing and the pulse widths of these signals are carefully controlled to adjust the pen-topen offsets, the bidirectional offsets, the pen-to-paper-axis deviation errors, and the pen turn-on energy variations.

The carriage ASIC contains three bus interfaces: the carriage processor (8052) bus, the serial link from the pen interface ASIC, and the pen driver IC interface. The block diagram of the IC is shown in Fig. 4. The processor bus is used to access the timing control registers. The serial data from the pen interface ASIC is shifted into a serial-to-parallel converter. A checksum counter monitors the serial input data to verify the integrity of the serial link. A parallel pipeline register follows the shift register to provide the double column buffering. The buffer outputs are divided into four delayed pipeline registers, each of which is delayed by the value in its corresponding delay time register. Each of the four data

**Fig. 3.** Pen interface ASIC block diagram.

Fig. 4. Carriage ASIC block diagram.

multiplexers selects the data to be driven for one half of each pen.

### **Design Approach and Tools**

Behavioral Simulation. The shuffler algorithm implemented in the pen interface ASIC and the carriage ASIC is a completely new design for any HP product. The shuffle path from the image data in the system memory to the pen outputs includes many hardware blocks and spans several different bus interfaces. The need to verify the correctness of the shuffler algorithm at a high level before any hardware design was apparent. A behavioral model of the algorithm was written in the C programming language. A graphics driver was added for both the input image data and the pen outputs. A complete graphical animation showed both the image data and the printed data as the pen swept across the screen. Any error in the shuffler algorithm was observable right on the display screen. This high-level verification approach turned out to be very valuable. The shuffler algorithm was completely debugged during the simulation phase before any hardware was designed.

**Emulator Strategy.** It was decided to build emulators for the three ASICs despite the substantial amount of additional resources required. As mentioned earlier, the functionalities of the ICs were needed before first silicon to enable parallel development of the printer mechanisms and the firmware. The emulators were able to meet this need. If there had